รายละเอียด Intel Skylake-X และ Skylake-SP Mesh Architecture

ทาง Intel ออกมาแชร์รายละเอียดถึง Skylake-SP และ Skylake-X series ที่เป็น processors ที่กำลังจะเปิดตัวในไม่ช้านี้. รายละเอียดได้เปิดเผย HEDT Skylake-X และ Xeon class Skylake-SP chips, ซึ่งใช้สถาปัตยกรรมตัวเดียวกัน, กล่าวได้เลยว่าทางด้านการดีไซน์นั้นมีการพัฒนาที่แตกต่างไปจากเมื่อ 9 ปีที่แล้วอย่างมาก.

Intel Skylake-X และ Skylake-SP มาพร้อมการอัพเกรดสถาปัตยกรรมใหม่อย่างก้าวกระโดด – ไม่ว่าจะเป็นทางด้าน Bandwidth, การใช้พลังงานที่ต่ำและ Lower Latency/ดีเลย์น้อย

หากย้อนกลับไปเมื่อสมัย Nehalem เปิดตัวออกมาเมื่อปี 2008, ทาง Intel ได้นำเสนอ (ณ ตอนนั้น) แนวการออกแบบ Ring Bus design สำหรับตัว processors. สำหรับรูปแบบ Ring Bus design ถูกออกแบบออกมาเพื่อรองรับการทำงานตัวชิปได้มากถึง 8 core Xeon processors. การต่อเชื่อมกันหรือ Ring bus inter connect สามารถวิ่งไปและกลับได้/bi-directional และช่องทางย่านความถี่and/sequential path และจะวิ่งผ่านตัวสำคัญที่สุดในตัว processor. ซึ่งจะรวมถึงตัวแกน, ตัวควบคุมบนบอร์ดหรือ integrated memory controllers, caches, PCI Express, I/O controllers, และอื่นๆอีก.

แบบวงแหวน ( Ring Topology ) เป็นการเชื่อมต่อเครือข่ายเป็นรูปวงแหวนหรือแบบวนรอบ โดยสถานีแรกเชื่อมต่อกับสถาน สุดท้าย การรับส่งข้อมูลในเครือข่ายจะต้องผ่านทุกสถานี โดยมีตัวนำสารวิ่งไปบนสายสัญญาณของแต่ละสถานี ต้องคอยตรวจสอบข้อมูลที่ส่งมา ถ้าไม่ใช่ของตนเองต้องส่งผ่านไปยังสถานีอื่นต่อไป

รูปแบบ Ring Bus มีข้อดีและการต่อเชื่อมกันและกันแบบง่ายๆจนกระทั่งทาง Intel เริ่มจะผลิต processors ที่มีจำนวนแกนที่มากๆ. สำหรับ Intel Xeon E5-2699 V4 เป็นรุ่นท๊อปสุดจากสาย Broadwell-EP Xeon (E5) ซึ่งมีจำนวนแกนมากถึง 22 cores. เป็นการอัพเกรดจาก 8 cores บน Nehalem. ปัญหาที่เกิดนั้นรูปแบบ single ring-bus ไม่สามารถรองรับแกนทั้งหมดได้, ดังนั้นจึงมีการทำออกมาเป็น 2 rings และใช้กับข้างใน die. die แต่ละตัวต้องการสื่อสารต่อกันเพื่อที่จะโอนถ่ายข้อมูลจาก ring วงที่สองไปยังวงแรก. ซึ่งวิธีการนี้ถูกนำมาใช้ใน bus ซึ่งสามารถรองรับการจราจรได้ทั้งสองทาง/bi-direction information / data transfer/ข้อมูลถ่ายโอนระหว่างกันของทั้งสองเซ็ดแกน.

เมื่อทั้งสองเซ็ตแกนนั้นใกล้กันและต่อเชื่อมกันผ่านทาง ring bus topology, โครงสร้างที่ได้ก็จะหนาแน่นและนั้นก็หมายถึงหากตัวข้อมูลนั้นต้องถูกตรวจสอบไม่ว่าจะเป็นส่วนไหนของ processor, ตัวชิปนั้นก็ต้องเริ่มจากวงแหวนหนึ่งไปอีกวงแหวนหนึ่ง. ซึ่งจะทำให้รอบการประมวลผลนั้นกินเวลามากขึ้นและดีเลย์เพิ่มซึ่งก็จะจบลงด้วยค่า bandwidth ไม่พอ.

และดูเหมือนรูปแบบ Ring Bus นั้นจะใช้ได้กับเฉพาะชิปที่มีแกนจำนวนไม่มากแต่ไม่ใช่สำหรับจำนวนแกนที่เยอะๆและอาจจะไม่เหมาะสำหรับในอนาคต. และยังไม่รวมถึงความต้องการทางด้าน I/O, PCI-Express ที่มีมากขึ้นโดยเฉพาะกับ Xeon และ HEDT class CPU รุ่นต่อไปและรูปแบบ Ring Bus นั้นก็คงจะไม่เหมาะเหตุเพราะจะยิ่งทำให้เกิดการดีเลย์ที่มากขึ้นรวมถึงการใช้พลังงานที่ไม่มีประสิทธิภาพ.

นำเสนอรูปแบบใหม่ Mesh Architecture – Intel ท้าชนเทคนิคของทาง AMD Infinity Fabric Interconnect

สำหรับสถาปัตยกรรมใหม่ของ Intel Mesh architecture ที่จะถูกบรรจุลงใน Skylake-SP และ Skylake-X processors นี้ต้องกล่าวว่าเป็นอะไรที่ออกมาท้าชนกับทาง AMD Infinity Fabric แบบตรงไปตรงมา. เราได้ยินเกี่ยวกับ AMD Infinity Fabric มากันบ้างแล้วเมื่อไม่กี่เดือนที่ผ่านมาก่อนที่จะเปิดตัว Ryzen processors. หากจำไม่ผิดก็ต้นปี 2017. สำหรับการพัฒนาและเปลี่ยนแนวทางด้านสถาปัตยกรรมนั้นไม่ใช่ใช้เวลาเพียงไม่กี่เดือนแต่ต้องมีอย่างน้อย 2-3 ปีขึ้นไป. ทาง Intel ได้นำเอาสถาปัตยกรรมใหม่มาแทนที่ Ring Bus inter connect ซึ่งถูกเปิดตัวเมื่อปี 2008 หรือเก้าปีที่แล้วซึ่งอันนี้เห็นได้ชัดว่าการพัฒนานั้นใช้เวลายาวนานมากว่าจะได้แนวทางใหม่มาซักตัว.

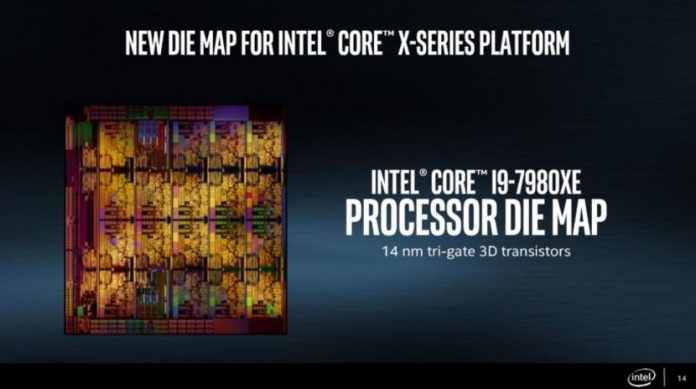

สำหรับ Skylake มันก็คือสถาปัตยกรรมใหม่ที่ถูกนำมาใช้และกำลังถูกนำไปใช้กับกลุ่ม HEDT และ Server ด้วยเช่นกันที่จะใช้กับจำนวนแกนที่มีมากหรือ multiple core count. และสำหรับ Mesh มันถูกสร้างขึ้นมาเพื่อ XCC dies หรือ Extreme Core Count processors ซึ่งจะเปิดตัวออกมาภายในเดือนนี้สำหรับ HEDT platforms และถัดไปก็เป็นสายของ Xeon.

คราวนี้เรามาดูของ Mesh, มันออกแบบเส้นทางมาแบบทั้งแนวตรงและแนวขนานหลายๆเส้นซึ่งจะต่อเชื่อมกับ cores, cache, memory controllers และ PCI Express. และยังมีการต่อเชื่อมภายในหรือ Inter-Socket Link ซึ่งมาแทนที่ QPI (Quick Patch Interconnect). ด้วยวีธีนี้ของ Mesh, ทาง Intel เพียงแค่คำนวนหรือคูณจำนวนช่องจราจรที่สื่อสารต่อกันเข้าไป ด้วยวิธีนี้ไม่เพียงเพิ่มค่า bandwidth แต่ยังลดทางด้านดีเลย์และความซับซ้อนหากเทียบกับแนวทางของ Ring Bus. สำหรับวิธีแบบ Mesh สามารถตรวจสอบผ่านทาง die โดยใช้เส้นทางที่มีมาให้อยู่มากและการเดินทางหรือรอบก็จะลดน้อยลงหากเทียบกับ ring bus. ซึ่งจะทำให้ชิปนั้นใช้ความเร็ว clock rates ที่ต่ำกว่าและแรงดันไฟน้อยลงส่วนทางด้านดีเลย์ก็จะต่ำตามมาพร้อมทั้ง band width ก็จะเพิ่มตามไปด้วย.

สำหรับทางด้านต้นทุนก็จะถูกลงและเพิ่มประสิทธิภาพให้กับตัวชิป. และยังไปลดเวลาการดีเลย์หรือ boosting latency times และความเร็ว bandwidth speeds ก็จะเพิ่มตามเมื่อมันถูกนำไปใช้กับชิปที่มีการดีไซน์จำนวนแกนที่มีมาก (มีมากถึง 28 cores บน Skylake-SP). จากภาพด้านบนคุณจะเห็นได้ว่าทาง Intel นั้นมี IMC (Integrated Memory Controllers)ทั้งซ้ายและขวาบน die. แต่ละข้างจะมีทั้งหมดสามแถว และยังบ่งบอกอีกด้วยว่าตัวนี้มันเป็นรุ่นตัดทอนลงมาของทาง die Xeon เพราะมันถูกออกแบบมาเพื่อรองรับได้ 6 channel memory (ต้นฉบับ). สำหรับ Skylake-X สามารถใช้ได้แค่ quad channel memory.

นอกเหนือไปกว่านั้น- Mesh มี PCI Express สองชุดหากเทียบกับ Ring ที่มีเพียงชุดเดียว. สรุปได้ว่า Mesh จะมี bandwidth ที่ดีกว่า, lower latency หรือดีเลย์น้อยกับรอบคำนวณและปริมาณงานที่อัดเข้าไปมากๆบน PCI Express lanes เช่นทางด้านกราฟฟิกการ์ด, NVMe SSDs รุ่นแรงๆหรือ 100 Gbps networks.

ภาพรวมสำหรับ Mesh architecture ดูแล้วจะทำมาเผื่อเอาไว้เลยในอนาคต-และแน่นอนว่าประสิทธิภาพของมันจะดีกว่าแต่ก่อนขนาดไหน. ที่แน่ๆ Skylake-X processors น่าจะเป็นคำตอบสำหรับเราแน่นอน.

ที่มาเครดิต/Sources:

http://wccftech.com/intel-skylake-x-skylake-sp-mesh-architecture-interconnect/

You must be logged in to post a comment.